**Prime**

# Assembly Language Programmer's Guide

Revision 21.0

DOC3059-2LA

# Assembly Language Programmer's Guide

**Second Edition**

by Len Bruns

This guide documents the software operation of the Prime Computer and its supporting systems and utilities as implemented at Master Disk Revision Level 21.0 (Rev. 21.0).

Prime Computer, Inc. Prime Park Natick, Massachusetts 01760 The information in this document is subject to change without notice and should not be construed as a commitment by Prime Computer, Inc. Prime Computer, Inc., assumes no responsibility for any errors that may appear in this document.

The software described in this document is furnished under a license and may be used or copied only in accordance with the terms of such license.

Copyright (C) 1987 by Prime Computer, Inc. All rights reserved.

PRIME, PRIME, PRIMOS, and the PRIME logo are registered trademarks of Prime Computer, Inc. DISCOVER, INFO/BASIC, INFORM, MIDAS, MIDASPLUS, PERFORM, Prime INFORMATION, PRIME/SNA, PRIMELINK, PRIMENET, PRIMEWAY, PRIMIX, PRISAM, PST 100, PT25, PT45, PT65, PT200, PW153, PW200, PW250, RINGNET, SIMPLE, 50 Series, 400, 750, 850, 2250, 2350, 2450, 2550, 2650, 2655, 2755, 6350, 6550, 9650, 9655, 9750, 9755, 9950, 9955, and 9955II are trademarks of Prime Computer, Inc.

#### PRINTING HISTORY

| First Edition  | (FDR3059-101) | March 1979 for Release 16.3   |

|----------------|---------------|-------------------------------|

| Update 1       | (COR3059-001) | January 1980 for Release 17.2 |

| Update 2       | (PTU2600-104) | June 1983 for Release 19.2    |

| Second Edition | (DOC3059-2LA) | July 1987 for Release 21.0    |

CREDITS

| Editorial:            | Thelma Henner  |

|-----------------------|----------------|

| Project Support:      | Margaret Taft  |

| Illustration:         | Mingling Chang |

| Document Preparation: | Celeste Henry  |

| Production:           | Judy Gordon    |

#### HOW TO ORDER TECHNICAL DOCUMENTS

To order copies of documents, or to obtain a catalog and price list:

#### United States Customers

#### International

Call Prime Telemarketing, toll free, at 1-800-343-2533, Monday through Friday, 8:30 a.m. to 5:00 p.m. (EST). Contact your local Prime subsidiary or distributor.

#### CUSTOMER SUPPORT

Prime provides the following toll-free numbers for customers in the United States needing service:

| 1-800-322-2838 | (within Massachusetts) | 1 - 800 - 541 - 8888 | (within Alaska) |

|----------------|------------------------|----------------------|-----------------|

| 1-800-343-2320 | (within other states)  | 1-800-651-1313       | (within Hawaii) |

For other locations, contact your Prime representative.

#### SURVEYS AND CORRESPONDENCE

Please comment on this manual using the Reader Response Form provided in the back of this book. Address any additional comments on this or other Prime documents to:

Technical Publications Department Prime Computer, Inc. 500 Old Connecticut Path Framingham, MA 01701

# Contents

## ABOUT THIS BOOK

ix

### 1 INTRODUCTION

2 USING PMA

| Invoking the Prime Macro   |     |

|----------------------------|-----|

| Assembler (PMA)            | 2-1 |

| File-naming Conventions    | 2-3 |

| Assembler Messages         | 2-4 |

| Listing Format             | 2-4 |

| Assembly Listing Symbology | 2-6 |

| Assignment Column Codes    | 2-6 |

| Instruction and Data       |     |

| Column Codes               | 2-6 |

| Other Listing Information  | 2-7 |

| Cross-reference Listing    |     |

| Symbology                  | 2-7 |

## 3 LANGUAGE STRUCTURE

| Statements3-2Statement Types3-2Statement Syntax3-3Continuation Lines3-3Statement Elements3-4Constants3-4Symbols3-4Terms and Expressions3-4Terms3-4Expressions3-4 |   |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| Statement Syntax3-3Continuation Lines3-3Statement Elements3-4Constants3-4Symbols3-4Terms and Expressions3-4Terms3-4                                              |   |

| Continuation Lines3-3Statement Elements3-4Constants3-4Symbols3-4Terms and Expressions3-4Terms3-4                                                                 |   |

| Statement Elements3-4Constants3-4Symbols3-4Terms and Expressions3-4Terms3-4                                                                                      | , |

| Constants3-4Symbols3-4Terms and Expressions3-4Terms3-4                                                                                                           | , |

| Symbols3-4Terms and Expressions3-4Terms3-4                                                                                                                       |   |

| Terms and Expressions3-4Terms3-4                                                                                                                                 |   |

| Terms 3-4                                                                                                                                                        |   |

|                                                                                                                                                                  |   |

| Expressions 3-4                                                                                                                                                  |   |

|                                                                                                                                                                  |   |

| Functions of Statement Fields 3-1                                                                                                                                | 0 |

| Label Field 3-1                                                                                                                                                  | 0 |

| Operation Field 3-1                                                                                                                                              | 1 |

| Operand Field 3-1                                                                                                                                                | 1 |

| Comment Field 3-1                                                                                                                                                | 3 |

| Pseudo-operations 3-1                                                                                                                                            | 3 |

| Machine Instructions 3-1                                                                                                                                         | 6 |

| Recommended Program Structure 3-1                                                                                                                                | 7 |

4 CODE GENERATION PSEUDO-OPERATIONS Assembly Control Pseudooperations (AC) 4-1 Conditional Assembly Pseudooperations (CA) 4-5 Symbol-Defining Pseudo-4-11 operations (SD) Listing Control Pseudooperations (LC) 4 - 145 CONSTANT DEFINITION PSEUDO-OPERATIONS Address Definition Pseudooperations (AD) 5-2 Data Definition Pseudooperations (DD) 5 - 4Storage Allocation Pseudooperations (SA) 5-12 6 LOADING AND LINKING PSEUDO-OPERATIONS Loader Control Pseudooperations (LC) 6-1 Program Linking Pseudooperations (PL) 6 - 47 MACRO DEFINITION PSEUDO-OPERATIONS Macro Definition Block 7-2 Macro Definition Pseudooperations (MD) 7-3 8 MACHINE INSTRUCTIONS -- V MODE Types of Addressing 8-1 Direct Address 8-2 Indexed Address 8-3 Indirect Address 8-3 Indirect Indexed Address 8 - 4Register Usage 8-6 Saving and Restoring Registers 8-7 Register Usage Between V Mode and I Mode 8-7 The V Mode Instruction Set 8-8 Generic Instructions 8-8 Branch Instructions 8 - 14Computed Go To Instruction 8-16 8-16 Jump Instructions

vi

Memory Reference Instructions

Process-related Operations

Restricted Instructions

8-19

8-30

8-32

| 9 | MACHINE | INSTRUCTIONS |  | I | MODE |

|---|---------|--------------|--|---|------|

|---|---------|--------------|--|---|------|

( (

| Types of Addressing             | 9-1   |

|---------------------------------|-------|

| Direct Address                  | 9-3   |

| Indexed Address                 | 9-3   |

| Indirect Address                | 9-3   |

| Indirect Indexed Address        | 9-4   |

| Addressing Through Registers    | 9-6   |

| Immediate Addressing            | 9-8   |

| Register Usage                  | 9-9   |

| Saving and Restoring Registers  | 9-9   |

| Register Usage Between          |       |

| I Mode and V Mode               | 9-9   |

| The I Mode Instruction Set      | 9-10  |

| Generic Instructions            | 9-11  |

| Branch Instructions             | 9-15  |

| Computed Go To Instruction      | 9-17  |

| Jump Instructions               | 9-18  |

| Memory Reference Instructions   | 9-20  |

| Process-related Operations      | 9-32  |

| Restricted Instructions         | 9-33  |

|                                 |       |

| MACHINE INSTRUCTIONS IX MODE    |       |

| Indirect Pointer-related        |       |

| Instructions                    | 10-1  |

| C Language-related Instructions | 10-3  |

|                                 | 10 5  |

| MACRO FACILITY                  |       |

| Macro Definition                | 11-2  |

| Argument References             | 11-2  |

| Assembler Attribute References  | 11-3  |

| Local Labels Within Macros      | 11-4  |

| Macro Calls                     | 11-4  |

| Argument Values                 | 11-5  |

| Argument Substitution           | 11-5  |

| Using Macro Calls as            |       |

| Documentation                   | 11-6  |

| Nesting Macros                  | 11-8  |

| Conditional Assembly            | 11-9  |

| Macro Listing                   | 11-9  |

| Assembler Attribute List        | 11-10 |

|                                 |       |

| USING SUBROUTINES               |       |

| Local Subroutines               | 12-1  |

| Local Calls in V Mode           | 12-2  |

| Local Calls in I Mode           | 12-5  |

| External Subroutines            | 12-7  |

| External Calls                  | 12-7  |

| Entrypoints to Called Routines  | 12-8  |

| Argument Passing in External    |       |

| Calls                           | 12-11 |

|                                 |       |

| Returning From an External Call | 12-11 |

|---------------------------------|-------|

| The Shortcall Mechanism         | 12-15 |

| General Considerations          | 12-15 |

| Argument Passing in V Mode      | 12-16 |

| Shortcall in I Mode             | 12-18 |

| Shortcalled Functions in        |       |

| V Mode and I Mode               | 12-20 |

### 13 LINKING AND LOADING

| Differences Between SEG and BIND | 13-2 |

|----------------------------------|------|

| Using the SEG Linker             | 13-2 |

| Using the BIND Linker            | 13-4 |

## 14 PROGRAM EXECUTION AND DEBUGGING

| Program Execution           | 14-1  |

|-----------------------------|-------|

| Program Debugging           | 14-2  |

| Using VPSD                  | 14-2  |

| VPSD Subcommand Line Format | 14-3  |

| VPSD Subcommands            | 14-6  |

| Using IPSD                  | 14-14 |

| Invoking IPSD               |       |

| Features Supported by IPSD  |       |

| but not VPSD                | 14-17 |

| Restrictions                | 14-20 |

| IPSD0 and IPSD16            | 14-21 |

|                             |       |

### APPENDICES

| A | ASSEMBLER ERROR MESSAGES        |      |

|---|---------------------------------|------|

| в | INSTRUCTION SUMMARY CHART       |      |

| с | PRIME EXTENDED CHARACTER SET    |      |

|   | Specifying Prime ECS Characters | C-2  |

|   | Direct Entry                    | C-2  |

|   | Octal Notation                  | C-2  |

|   | Character String Notation       | C-2  |

|   | Special Meanings of Prime ECS   |      |

|   | Characters                      | C-5  |

|   | Assembly Programming            |      |

|   | Considerations                  | C-6  |

|   | Prime Extended Character Set    |      |

|   | Table                           | C-6  |

|   |                                 |      |

|   | INDEX                           | X-1  |

|   |                                 |      |

|   | COMPOSITE INDEX                 | CX-1 |

|   |                                 |      |

# **About This Book**

The <u>Assembly Language Programmer's Guide</u>, Second Edition, documents the use of the Prime Macro Assembler (PMA) as implemented at PRIMOS Revision 21.0. It replaces the first edition of the same guide and its various updates. It is a completely rewritten guide, whose salient features are

- Reorganization of the text into a sequence of chapters that more closely parallels an actual assembly. Introductory chapters give an overview of the assembler and describe its invocation and command line options. The remaining chapters discuss coding the program, defining and calling macros and subroutines, linking the program, executing, and debugging.

- Removal of most material that is duplicated in other volumes. Where required for an understanding of the subject under discussion, this material has been replaced by references to the appropriate manuals. This guide is, therefore, a more compact but no longer self-contained reference text; it is intended to be used in conjunction with other manuals. A list of reference documents appears later in this preface.

- Elimination of discussions of S mode and R mode. Use of these older addressing modes is declining, and the user is urged to do all new programming in the current V, I, and IX addressing modes. For those users who need to maintain existing S-mode and R-mode programs, the relevant information in the first edition of this guide is still valid. The <u>System Architecture Reference</u> <u>Guide</u> and the <u>Instruction Sets Guide</u> also continue to present information on S mode and R mode.

#### Summary of Chapters and Appendices

This book contains the following chapters and appendices:

Chapter 1 is an overview of the current implementation of the assembler; Chapter 2 describes its method of invocation and the various command line options available.

Chapter 3 is a detailed description of the language elements: statements and their components; terms and expressions; and the functions of statement components and fields.

Chapters 4 through 7 discuss the coding of the four major categories of pseudo-operations and their functions and requirements.

Chapters 8 through 10 discuss, respectively, the instruction sets for V mode, I mode, and IX mode.

Chapter 11 describes the coding and calling of macro routines and the logic capabilities of macro processing, while Chapter 12 is devoted to several methods of calling local and external subroutines.

Chapter 13 discusses simple linking of assembled programs using the SEG and BIND linkers, with references to other documents for more complex linking tasks.

Chapter 14 briefly describes the invocation of linked programs, and goes on to discuss V-mode and I-mode debugging in some detail.

Three appendices provide reference material in the form of a list of assembler error messages (Appendix A); a summary of the V, I, and IX mode instruction sets (Appendix B); and a description of the Prime Extended Character Set (Prime ECS) and its use (Appendix C).

#### Reference Documents

The following guides are frequently referred to in the text of this book.

System Architecture Reference Guide, DOC9473-2LA

Instruction Sets Guide, DOC9474-2LA

SEG and LOAD Reference Guide, DOC3524-192 and update, UPD3524-21A, for Rev. 19.4

Programmer's Guide to BIND and EPFs, DOC8691-1LA

Advanced Programmer's Guide, Vol. I: BIND and EPFs, DOC10055-1LA

Advanced Programmer's Guide, Vol. II: File System, DOC10056-2LA

Advanced Programmer's Guide, Vol. III: Command Environment, DOC10057-1LA

- Advanced Programmer's Guide, Vol. 0: Introduction and Error Codes, DOC10066-2LA

- Subroutines Reference Guide, Vol. I: Language Interface, DOC10080-2LA

- Subroutines Reference Guide, Vol. II: File System, DOC10081-1LA and update, UPD10081-11A

- Subroutines Reference Guide, Vol. III: Operating System, DOC10082-1LA and update, UPD10082-11A

- Subroutines Reference Guide, Vol. IV: User Libraries, DOC10083-1LA and update, UPD10083-11A

### PRIME DOCUMENTATION CONVENTIONS

The following conventions are used in command formats, statement formats, and in examples throughout this document. Examples illustrate the uses of these commands and statements in typical applications.

| Convention                                       | Explanation                                                                                                                                                                                         | Example                                                                                                                   |

|--------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|

| UPPERCASE                                        | In command formats, words<br>in uppercase indicate the<br>names of commands, options,<br>statements, and keywords.<br>Enter them in either upper-<br>case or lowercase.                             | SLIST                                                                                                                     |

|                                                  | In PMA statements, upper-<br>case elements are entered<br>exactly as shown, and only<br>in uppercase.                                                                                               | DATA value                                                                                                                |

| lowercase                                        | In command formats and PMA<br>statements, words coded in<br>lowercase indicate vari-<br>ables for which you must<br>substitute a value.                                                             | LOGIN user-id<br>DATA value                                                                                               |

| Abbreviations<br>in format<br>statements         | If an uppercase word in a<br>command format has an ab-<br>breviation, either the ab-<br>breviation is underscored or<br>the name and abbreviation<br>are placed within braces.                      | <u>LO</u> GOUT<br>{    SET_QUOTA }<br>SQ }                                                                                |

| Brackets<br>[ ]                                  | Brackets enclose a list of<br>one or more optional items.<br>Choose none, one, or more of<br>these items.                                                                                           | LD -BRIEF<br>-SIZE                                                                                                        |

| Braces { }                                       | Braces enclose a list of items. Choose one and only one of these items.                                                                                                                             | $\begin{array}{c} \text{CLOSE} & \left\{ \begin{array}{c} \text{filename} \\ \text{ALL} \end{array} \right\} \end{array}$ |

| Vertical bars<br>within<br>brackets<br>[*A B C ] | Vertical bars within brack-<br>ets offer a choice among two<br>or more items. Choose either<br>none or one of these items;<br>do not choose more than one.<br>Asterisked value is the de-<br>fault. | -L [*YES NO TTY]                                                                                                          |

| Convention                           | Explanation                                                                                                   | Example                                                                  |

|--------------------------------------|---------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|

| Ellipsis<br>                         | An ellipsis indicates that<br>the preceding item may be<br>entered more than once in<br>a format.             | DATA value,                                                              |

| Parentheses<br>()                    | In command or statement for-<br>mats, you must enter paren-                                                   | SPOOL FILE(1 2 3)                                                        |

|                                      | theses exactly as shown.                                                                                      | XFER MAC (FROM)=1                                                        |

| Hyphen<br>-                          | Wherever a hyphen appears<br>as the first character of an<br>option, it is a required<br>part of that option. | SPOOL -LIST                                                              |

| <u>Underscore</u><br>in examples     | In examples, user input is<br>underscored but system<br>prompts and output are not.                           | OK, <u>RESUME MY_PROG</u><br>This is the output<br>of MY_PROG.CPL<br>OK, |

| Apostrophe<br>'                      | An apostrophe preceding a<br>number indicates that the<br>number is in octal.                                 | <b>'</b> 200                                                             |

| Angle brackets<br>in examples<br>< > | In examples, the name of a<br>key enclosed within angle<br>brackets indicates that you<br>press that key.     | OK, <u>ED</u> <return></return>                                          |

(

(

# 1 Introduction

The Prime Macro Assembler (PMA) at PRIMOS Revision 21.0 incorporates several enhancements over previous versions. Some of these are related to the operation of the assembler itself, while others are concerned with new PRIMOS and hardware facilities. The following items describe the enhancements.

- The assembler is capable of assembling much larger object programs than in the past, owing to a new method of storing the symbol table. Symbol table size has until now been limited by the bounds of a single segment that also contains the assembler's executable code. The new storage mechanism uses a segment apart from the execution segment; moreover, it is capable of adding more symbol storage segments when the need arises.

- Two assembler attributes that were previously designated as <u>spare</u> are no longer so designated. Assembly language programmers who used these attributes for their own purposes can no longer do so. Attribute #108 is designated as <u>reserved</u>, while attribute #111 contains a parity value established by whether the length of the character string defined by the most recent DATA, BCI, or BCZ pseudo-operation was even (parity is 0) or odd (parity is 1). Assembler attributes are listed in Chapter 11.

- In addition to formerly-supported S, R, V, and I address modes, IX mode is supported as of Revision 21.0. IX mode operates on 50 Series Models 2550TM 9650TM 9750TM 9950TM 9955TM and 9955IITM It includes a small set of additional instructions that enable operations involving C language pointers and characters. These instructions are described in Chapter 10.

- The assembler supports an I mode addressing enhancement that permits a general-register-relative format in memory reference instructions and adds two indirect pointer related instructions, AIP and LIP. GRR format (described in Chapter 9) improves the performance of programs that must address large arrays that could potentially cross segment boundaries. This format operates only on the 50 Series models listed for IX mode in the preceding paragraph.

- The assembler supports the Prime extended character set (Prime ECS). The extended character set and its implications for assembly-language programs are described in Appendix C.

- A new subroutine calling mechanism, <u>shortcall</u>, is described in Chapter 12. Shortcall provides a much faster transfer of control to and from a PMA-written subroutine than the traditional PCL/PRTN mechanism. Shortcall, from a high-level language caller's point of view, is currently implemented only in Fortran 77. I-mode PMA shortcalled routines can take advantage of GRR, register-to-register, and immediate addressing formats to further enhance overall program efficiency.

- The assembler produces binary files that are compatible with the BIND linker, introduced at Revision 19.4, to create runfiles in executable program (EPF) format. A description of a simple BIND session appears in Chapter 13.

# 2 Using PMA

The Prime Macro Assembler (PMA) is a three-pass assembler. The first pass creates a symbol table containing internal symbols and their segment-relative displacements, and identifies external references. The second pass uses the symbol table to resolve references to the internal symbols, generates object code blocks for input to the linker and, optionally, creates a listing. The third pass permits optimization of stack and link frame references.

#### INVOKING THE PRIME MACRO ASSEMBLER (PMA)

PMA is invoked by the command:

PMA pathname [-option-1] [-option-2]...[-option-n]

<u>pathname</u> specifies the pathname of your source PMA program. The standard pathname conventions apply. File naming conventions are described following the option descriptions. PMA supports the following options. Default options are indicated by asterisks (\*).

-BINARY, -B [\* YES|NO|pathname] -RESET -ERRLIST -ROUND \* -EXPLIST \*-XREFL -INPUT [pathname], -I [pathname] -XREFS -LISTING, -L [\* YES|NO|TTY|SPOOL|pathname]

Brief descriptions of these options are given below.

-BINARY [\* YES|NO|pathname]

Specifies binary (object) file.

[YES] gives <u>source-program.BIN</u> if source program name has .PMA suffix, otherwise gives <u>B\_source-program</u>. Binary file is in the home directory.

[NO] gives no binary file.

[pathname] allows complete specification of binary file.

-ERRLIST

Generates errors-only listing (overrides pseudo-operation NLIST).

\* -EXPLIST

Generates full assembly listing (overrides pseudo-operation NLIST).

-INPUT [pathname]

Specifies source program.

[pathname] is the name of source program. (Do not use if name immediately follows the PMA command). Standard pathname conventions apply.

-LISTING [\* YES | NO | TTY | SPOOL | pathname]

Specifies listing file.

[YES] gives <u>source-program.LIST</u> if source program has .PMA suffix, otherwise gives <u>L\_source-program</u>. Listing file is in the home directory.

[NO] gives no listing file.

[TTY] displays assembly listing at the terminal.

[SPOOL] puts listing file into line printer spool queue.

[pathname] allows complete specification of listing file.

-RESET

Resets A, B, and X Register settings.

-ROUND

Rounds rather than truncates conversion of real numbers to decimal.

\* -XREFL

Generates complete cross reference listing.

-XREFS

Omits from cross reference list symbols that are defined but not used.

#### FILE NAMING CONVENTIONS

For consistency with Prime's other language processors, the pathname of the source file should be suffixed with a language name code. For the assembler, the code is .PMA. The form of the source filename affects the form of the default names of the binary and listing files: if the source filename suffix is not .PMA, the default binary and listing filenames are <u>prefixed</u> by B\_ and L\_, respectively; if the source filename suffix is .PMA, the default binary and listing filenames are <u>suffixed</u> by .BIN and .LIST, respectively. The .PMA form is recommended, both for consistency and for ease of use in subsequent operations such as linking and invoking the resulting programs.

The defaults for both binary and listing filenames can be overridden by specifying different pathnames as arguments to the -BINARY and -LISTING options, respectively. The -LISTING option also accepts TTY as an argument to cause the assembly listing to appear at your terminal.

#### FILE USAGE

Three files may be involved during an assembly:

| <u>File Type</u> | PRIMOS File unit |

|------------------|------------------|

|                  |                  |

| Source           | 1                |

| Listing          | 2                |

| Binary           | 3                |

PMA automatically opens files for listing and binary output. They are closed at the termination of each assembler run.

The PRIMOS commands LISTING and BINARY permit you to concatenate two or more listing files, and two or more binary files, respectively. These commands, when used before a series of PMA invocations, open file units 2 (for the listing file) and 3 (for the binary file). The assembler uses them to write the files, and leaves them open when it returns control to PRIMOS. Each subsequent invocation of the assembler appends its listing and binary outputs to those already written. The files can be closed by use of the PRIMOS CLOSE command. Refer to the <u>PRIMOS</u> <u>Commands Reference Guide</u> for descriptions of these commands.

#### ASSEMBLER MESSAGES

After the assembler processes a program's END statement, it prints a message, terminates assembly, and returns control to PRIMOS command level. The message contains a decimal error count, the assembler version number, and a copyright statement:

<nn> ERRORS [PMA <version> Copyright (c) Prime Computer, Inc. <year>]

#### LISTING FORMAT

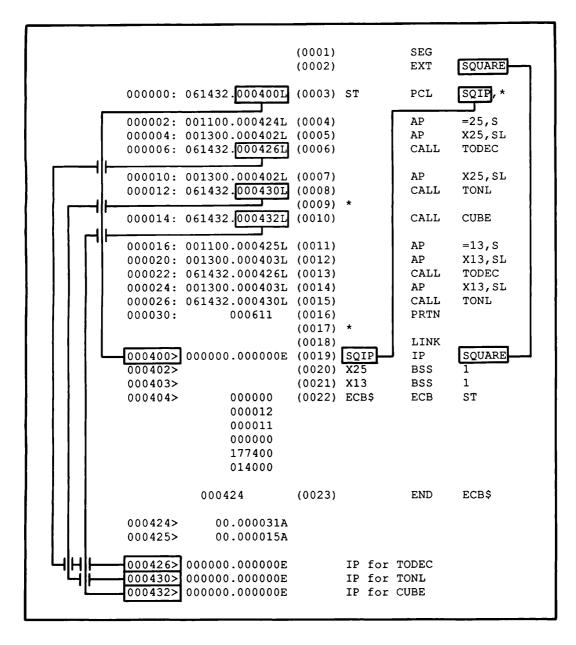

Figure 2-1 shows a section of a typical assembly listing and illustrates the main features.

When the assembly listing file is printed using the SPOOL command with no options, each page begins with a header and contains a page number. (Some Spooler options disable headers and pagination; refer to the description of the SPOOL command in the <u>PRIMOS Commands Reference</u> <u>Guide</u>.) The first statement in a program is used as the initial page header. If column 1 of any source statement contains an apostrophe ('), columns 3 through 80 of that statement become the header for all pages that follow, until a new header is specified.

At the end of the assembly listing appears a cross reference table containing each symbol's name (in alphabetical order), the symbol's address value with a code indicating the segment in which it resides, and a list of all line numbers defining or referring to the symbol. The address values are in octal unless the PCVH pseudo-operation specifies hexadecimal listing. Each reference is identified by a four-digit line number. The NLST pseudo-operation suppresses the cross reference listing; the -XREFS option suppresses symbols which have been defined but not used.

|          | SEG            | (0001) | ' SA        | FIFLE AS | SEMBLER L | TOTTING |

|----------|----------------|--------|-------------|----------|-----------|---------|

|          | 369            | (0001) |             | SEG      |           |         |

| 000000:  | 02.000015      | • •    | START       | LDA      | м         |         |

| 0000001: |                | (0002) | START       | MPY      | X         |         |

|          |                | • •    |             |          |           |         |

|          | 015414.000017  | (0004) |             | ADL      | В         |         |

| 000004:  |                | (0005) |             | PIMA     |           |         |

| 000005:  |                |        |             | STA      | OUT       |         |

|          | 061432.0004221 |        |             | CALL     | TODEC     |         |

|          | 001300.0004001 |        |             | AP       | OUT,SL    |         |

|          | 061432.0004241 |        |             | CALL     | TONL      |         |

| 000014:  | 000611         | (0010) |             | PRTN     |           |         |

| 000015:  | 000003         | (0011) |             | DATA     | 3         |         |

| 000016:  | 000005         | (0012) | х           | DATA     | 5         |         |

| 000017:  | 000000         | (0013) | В           | DATA     | 10L       |         |

| 000020:  | 000012         |        |             |          |           |         |

|          |                | (0014) |             | LINK     |           |         |

| 000400>  | 000000         | (0015) | OUT         | DEC      | 0         |         |

| 000401>  | 000000         | (0016) | ECB\$       | ECB      | START     |         |

|          | 000012         |        |             |          |           |         |

|          | 000011         |        |             |          |           |         |

|          | 000000         |        |             |          |           |         |

|          | 177400         |        |             |          |           |         |

|          | 014000         |        |             |          |           |         |

|          |                |        |             |          |           |         |

|          | 000421         | (0017) |             | END      | ECB\$     |         |

| 000421>  | 00.000002      | A      |             |          |           |         |

| 000422>  | 000000.00000B  | 3      |             |          |           |         |

| 000424>  | 000000.000000  | 2      |             |          |           |         |

| TEXT SI2 | ZE: PROC 0000  | 21 LI  | NK 000026   | STAC     | K 000012  |         |

| в        | 000017 0004    | 0013   |             |          |           |         |

| ECB\$    | 000401L 0016   |        |             |          |           |         |

| M        | 000015 0002    |        |             |          |           |         |

| OUT      | 000400L 0006   |        | 0015        |          |           |         |

| START    | 000000 0002    |        | ~~ <b>1</b> |          |           |         |

| TODEC    | 000000E 0007   |        |             |          |           |         |

| TONL     | 000000E 0007   |        |             |          |           |         |

| X        | 000016 0003    |        |             |          |           |         |

| Λ        | 000016 0003    | 0012   |             |          |           |         |

|          |                |        |             |          |           |         |

**[**

(

Sample Assembler Listing Figure 2-1

#### ASSEMBLY LISTING SYMBOLOGY

The first two columns of an assembly listing show the octal representations of the addresses the assembler assigns to each area allocated for storage of machine instruction or data strings, and the generated strings themselves, if any. Appended to each entry in these columns is a code (a blank is considered a code). These codes are described in the following two sections.

#### Assignment Column Codes

The codes in the first assembly listing column indicate the segment to which the assembler assigns the accompanying generated string. The meanings of the codes are:

: String is assigned to the procedure segment > String is assigned to the linkage segment

The assembler can also allocate space in the stack segment (by a DYNM pseudo-operation); these assignments have no entry in the first column, but have their stack-relative addresses listed in the second column with a blank assignment code.

#### Instruction and Data Column Codes

The second assembly listing column contains the assembler-generated instruction or data string. Its entries vary in length.

For data strings an entry contains six octal digits and represents one halfword (16 bits) of storage. For pseudo-operations such as DYNM, EQU, ORG, and END, it can also represent a 16-bit quantity that can be interpreted as either a numeric constant or an address, depending on how the assembler uses it. The entry is terminated by a blank.

For generic instructions (those that do not reference memory) an entry contains six digits and represents a 16-bit octal operation code. For memory reference instructions an entry consists of two parts separated by a period. The first part represents the operation code and contains two digits (for short-form instructions) or six digits (for long-form instructions). The second part represents a referenced memory address and is followed by a code indicating the storage class of the addressed item. The codes associated with the instruction and data column have the following meanings:

| blank | Addressed item is relative to the current module      |

|-------|-------------------------------------------------------|

| A     | Addressed item is an absolute number                  |

| Е     | Addressed item is external to the program             |

| L     | Addressed item is relative to the linkage base (LB)   |

| P     | Addressed item is relative to the procedure base (PB) |

| R     | Addressed item is relative to a general register      |

|       | (I mode only)                                         |

| S     | Addressed item is relative to the stack base (SB)     |

| х     | Addressed item is relative to the auxiliary base (XB) |

#### Other Listing Information

The remainder of the assembly listing consists of source program line images and, shown in parentheses, the assembler-assigned line number of each statement. These line numbers are for the benefit of the cross reference listing, described in the next section.

#### CROSS REFERENCE LISTING SYMBOLOGY

The cross reference listing shows, for each symbol defined or referenced in a program, the symbol name, its storage address and class, and one or more numbers indicating the statement line number in which it is defined or referenced.

The storage class codes that can appear in a cross reference listing are the same as those that can appear in the instruction and data column of the assembly listing; their meanings are also the same.

# 3 Language Structure

This chapter describes the structure and function of Prime Macro Assembler language statements and the elements with which they are constructed.

The PMA language structure is both flexible and simple. For example, here is a program which includes three pseudo-operations, a machine instruction and a literal.

| SEG       | Pseudo-operation assemble in V-mode                 |

|-----------|-----------------------------------------------------|

| LDA ='301 | Machine instruction with literal operand            |

| CALL TIOB | Pseudo-operation subroutine call (generates machine |

|           | instruction).                                       |

| END       | Pseudo-operation defines end of source code.        |

#### LINES

Input to the assembler consists of statement, comment, and header lines. The basic unit of information is the line, which consists of fields separated by spaces. Line syntax is described later in this chapter.

All lines except comment and header lines must be entered in uppercase characters. Comment lines, header lines, and the comment fields of statement lines can be in uppercase or lowercase.

There are three basic line formats:

| Comment Line | Column 1 contains an asterisk (*). The entire line is treated as a comment.                                   |

|--------------|---------------------------------------------------------------------------------------------------------------|

| Header Line  | Column 1 contains an apostrophe ('). The rest of<br>the line is used as a page title for subsequent<br>pages. |

| Statement    | Statements are described in the following sections.                                                           |

#### STATEMENTS

Every statement causes the assembler either to generate machine code (instructions or data) or to take some assembler or linker related action.

#### Statement Types

There are four kinds of statements:

Machine instructions

Generate the instructions and data the program is to execute and use. Machine instructions are fully described in Chapters 8, 9, and 10, and in the <u>Instruction Sets Guide</u>.

#### Pseudo-operations

Direct the assembler to perform some function during an assembly. With few exceptions, they do not generate machine instructions; they do, however, frequently generate data. Pseudo-operations are described in Chapters 4 through 7.

#### Macro definitions

Delimit blocks of code or data (or both) that can be called as if they were instructions. This group also contains some pseudo-operations that provide a logic capability within a macro definition block. See Chapter 7.

Macro calls

Invoke code previously defined in macro definitions. These are described in Chapter 11.

Statement Syntax

Statements can have up to four fields, delimited by spaces:

[label] operation [operand]... [comment]

- label The first character of a label must be in column 1 of a line. If a statement does not have a label, the first column must be blank. Labels are from 1 to 32 characters in length. The first character is a letter (A through Z), and the remaining characters can be letters, numerals (0 through 9), the dollar sign (\$), or underscore (\_).

- operation The operation field is the only field required in all types of instructions. It contains the mnemonic code for a machine instruction or a pseudo-operation. It is separated from the label field, if any, by one or more spaces.

- operand The number of operands and their meanings are operation-specific. Some statements do not require an operand, while others require one or more. The first operand is separated from the operation code by one or more spaces; multiple operands are separated by commas, and there must be no intervening spaces unless an operand is a literal that contains spaces. Literal operands and operands defining character constants can contain any character in the Prime ECS character set (see Appendix C).

- comments All text following either column 72 or two spaces after the last operand (10 spaces or following a colon in macro calls) is treated as a comment. Comments can contain any character in the Prime ECS character set.

#### Continuation Lines

Any statement can be interrupted by a semicolon (;) and continued on the next line. Any text following the semicolon is treated as a comment. Processing of the statement continues with the first nonspace character in the following line. Semicolons appearing within comments are not interpreted as continuation indicators. A semicolon that appears as a character in a literal must be preceded by the assembler's escape character, the exclamation point (!).

#### STATEMENT ELEMENTS

Statement elements -- labels, operation codes, and operands -- are composed of constants and symbols. These are made up of the subset of the printing ASCII characters defined for labels, above. The entire Prime extended character set (Prime-ECS), printing and nonprinting, can be used in comments, macro instruction operands, literals, and constants. Refer to Appendix C for a discussion of Prime-ECS.

#### Constants

Constants are explicit data values. They are most often used in operands of data-defining pseudo-operations and in literal operands. They can be used to represent bit configurations, absolute addresses, program-relative addresses (displacements), and data. A constant may be any of the following data types:

Decimal Binary Hexadecimal Octal Character Address

#### Symbols

Symbols are alphanumeric strings which represent locations or data. They may be from 1 to 32 characters in length. The first character must be a letter (A through Z), and the remaining characters may be letters, numerals (0 through 9), the dollar sign (\$), or underscore (\_). Symbols containing more than 32 characters are allowed in the source code, but only the first 32 characters are examined by the assembler.

#### TERMS AND EXPRESSIONS

An operand can be constructed of one or more elements called <u>terms</u>, combined into an <u>expression</u> by use of one or more <u>operators</u>. These are described in this section.

#### Terms

A term is the smallest element that represents a distinct value. It represents a single precision signed integer and may be a constant or a symbol.

Second Edition

Every term, whether used alone or in an expression, has both a value and a mode. These attributes either are defined by the assembler and related to the procedure, stack, link, or common location counter, or they are inherent in the term itself. Symbols defined by the EQU, SET, and XSET pseudo-operations receive both the mode and the value of the term or expression in their operand fields; labels, at the time of their definition, take the mode and value of the current location counter. Refer to the description of the ORG statement in Chapter 4 for a discussion of how the mode of the location counter is set). Some examples of terms are:

- '123 Octal constant

- C'A' Character (string) constant

- BETA Symbol

- 1.23E2 Invalid because it is a floating point number; it does not have a single precision integer value

- C'ABC' Invalid because the value is too large for 16 bits

<u>Value of a Term</u>: The value of a term is its single precision numeric equivalent. It can represent either an address relative to some base in the program or an absolute number. Some examples of symbolic term definitions, usages, and values are shown below.

| Symbol | Usage           | Explanation                                                                                                   |  |  |

|--------|-----------------|---------------------------------------------------------------------------------------------------------------|--|--|

| LABSYM | LABSYM LDA LOC  | LABSYM is a label symbol whose value<br>is the address (program counter value)<br>of the instruction LDA LOC. |  |  |

| DATSYM | DATSYM DATA '10 | DATSYM is a label symbol whose value<br>is the address (program counter<br>value) of the constant '10.        |  |  |

| ADSYM  | ADSYM DAC LOC   | ADSYM is a label symbol whose value<br>is the address (program counter<br>value) of the address constant LOC. |  |  |

| ABSSYM | ABSSYM EQU '10  | ABSSYM is a symbol whose value is '10.                                                                        |  |  |

| CHRSYM | CHRSYM EQU C'A' | CHRSYM is a symbol whose value is<br>A <space> ('140640).</space>                                             |  |  |

<u>Mode of a Term</u>: The mode of a term defines whether the value associated with a symbol is absolute or relative to some base. A term can have one of the following modes:

- Absolute The value of the symbol is independent of its position relative to any base. Symbols equated to absolute terms or to the results of expressions involving only absolute terms have a mode of absolute.

- Procedure Relative The symbol is defined relative to the start of the module; it is identified by an asterisk if the current location counter's mode is procedure relative, or by reference to another procedure relative label.

- Common Relative The symbol is defined relative to a data area defined by a COMM pseudo-operation. This data area can be shared by several independently assembled or compiled routines.

- External The symbol is defined in a separately assembled module and is identified in the current module by an EXT pseudo-operation.

- Stack Base Relative The symbol is defined relative to the start of the current program's stack area. Variables defined by the DYNM pseudo-operation or by <u>SB% + value</u> have a mode of stack relative.

Procedure Absolute The symbol is defined relative to the start of the procedure segment and is identified by PB% + value.

- Linkage Base Relative The symbol is defined relative to the start of the program's linkage area and is identified by LB% + value, or \* if the current location counter's mode is linkage relative.

- Auxiliary Base Relative The symbol is defined relative to the contents of the auxiliary base register and is identified by <u>XB% + value</u>.

The mode of a term is represented internally in the assembler by a number from 0 through 7. The modes and their numeric equivalents are:

0 Absolute 1 Procedure relative 2 Common 3 External Stack base relative 4 5 Procedure absolute 6 Linkage base relative 7 Auxiliary base relative

A term's mode number can be represented in an assembly statement by prefixing the symbol with a left bracket ([):

#### [ABC

It is thus possible to determine, for example, whether the mode of the term ABC is stack base relative or linkage base relative by a sequence such as

MODE SET [ABC IF MODE .EQ. 4 statement\_1 IF MODE .EQ. 6 statement\_2

The assembler generates statement\_1 if ABC is a stack based label, or statement\_2 if it is a linkage based label.

Refer to the discussion of conditional assembly in Chapter 4 for a description of the use of IF and other conditional statements.

#### Expressions

Expressions contain one or more terms (constants or symbols) joined by operators. Expressions may contain arithmetic, logical, relational and shift operators.

<u>Arithmetic Operators</u>: Perform addition, subtraction, multiplication, and division operations:

| <u>Operator</u> | Meaning        | Example                  | <u>Result (Octal)</u> |

|-----------------|----------------|--------------------------|-----------------------|

| +               | Addition       | <b>'</b> 3+ <b>'</b> 4   | 000007                |

| -               | Subtraction    | 10-13                    | 000005                |

| *               | Multiplication | <b>'</b> 20* <b>'</b> 10 | 000200                |

| 1               | Division       | '23/'10                  | 000002                |

Division retains only the integer part of the quotient.

Logical Operators: Perform a logical operation on two 16-bit operands:

| <u>Operator</u> | Meaning                 | Example       | Result (Octal) |

|-----------------|-------------------------|---------------|----------------|

| .OR.            | Logical OR              | '123.OR.'456  | 000577         |

| .XOR.           | Logical<br>Exclusive OR | '123.XOR.'456 | 000575         |

| .AND.           | Logical AND             | '123.AND.'456 | 000002         |

<u>Relational Operators</u>: Perform a comparison of two 16-bit operands with a result of 0 if false and 1 if true.

| <u>Operator</u> | <u>Relation</u>          | Example                      | Result (Octal)   |

|-----------------|--------------------------|------------------------------|------------------|

| .EQ.            | equal                    | '123.EQ.'123<br>'123.EQ.'456 | 000001<br>000000 |

| .NE.            | not equal                | '123.NE.'123<br>'123.NE.'456 | 000000<br>000001 |

| .GT.            | greater than             | '123.GT.'123<br>'456.GT.'123 | 000000<br>000001 |

| .GE.            | greater than<br>or equal | '123.GE.'123<br>'123.GE.'456 | 000001<br>000000 |

| .LE.            | less than<br>or equal    | '123.LE.'123<br>'123.LE.'456 | 000001<br>000001 |

| .LT.            | less than                | '123.LT.'456<br>'456.LT.'123 | 000001<br>000000 |

<u>Shift Operators</u>: Perform logical right or left shift of an expression, using the syntax:

argument-expression .LS. shift-count-expression .RS.

| <u>Operator</u> | Meaning     | Example    | <u>Result (Octal)</u> |

|-----------------|-------------|------------|-----------------------|

| .LS.            | Left Shift  | '123.LS.'3 | 001230                |

| .RS.            | Right Shift | '123.RS.'3 | 000012                |

Expression Conventions: The following conventions apply to the construction of expressions.

Spaces Operators can be preceded and followed by a single space (more than one space causes the assembler to treat the rest of the line as a comment).

- Signs The operands for arithmetic operators may be signed.

- Operator Priority In expressions with more than one operator, the operator with the highest priority is performed first. In cases of equal priority, the evaluation proceeds from left to right. Parentheses can be used to alter the order of evaluation.

| <u>Priority</u> | Operator |              |  |

|-----------------|----------|--------------|--|

| Highest         | * /      |              |  |

|                 | + -      |              |  |

|                 | .RS.     | .LS.         |  |

|                 |          | .GE.<br>.LE. |  |

|                 | .AND.    |              |  |

|                 | .OR.     |              |  |

| Lowest          | .XOR.    |              |  |

<u>Resultant Mode</u>: For all operations except addition and subtraction, both operands' modes must be absolute; the resultant mode is absolute.

When an addition operator is used, no more than one of the terms can be relative. If one term is relative, the resultant mode is the mode of the relative term; if all terms are absolute, the resultant mode is absolute.

When a subtraction operator is used, one or both terms can be relative. If both are relative, they must be relative to the same base; the resultant mode is absolute. When one term is relative, it must be the first term; the resultant mode is the mode of the relative term.

For multiplication and division, both terms must be absolute; the resultant mode is absolute. For division, if the resultant value is not an integer, the fractional part is discarded and the value is the integer part.

#### FUNCTIONS OF STATEMENT FIELDS

This section describes the functions of the four fields of all assembly language statements.

#### Label Field

The label field equates a symbolic name appearing within it to a numeric value. The value can represent either the address of a program element (instruction or data) or a numeric constant. In either case, the value is a 16-bit integer quantity, and can range from 0 through 65535 decimal (0 through 177777 octal), inclusive.

A symbolic name is defined when it appears in a statement's label field. It is referenced when it appears in an operand field. This means that when a symbolic name, or label, appears in the label field, the assembler <u>assigns</u> a value to the name. The value assigned depends on the type of statement. For an instruction statement, the value is the location of the instruction relative to the start of the program. For a psuedo-operation, the value depends on the function of the pseudo-operation (See Chapters 4 through 7 for descriptions of these functions.)

When a label appears in the operand field of a statement, the assembler retrieves the assigned value and substitutes it for the symbolic name. For all machine instructions and most pseudo-operations, the relative placement in a program of statements that define labels and those that reference them is immaterial. A few pseudo-operations, however, require that labels used in their operand fields be defined before they are referenced. These requirements will be indicated where appropriate in the descriptions of pseudo-operations later in this guide.

#### Operation Field

The operation field of a statement contains the mnemonic operation code of an instruction or a pseudo-operation. An instruction mnemonic causes the generation of a machine instruction; a pseudo-operation mnemonic causes the assembler to take some action which may or may not result in the generation of machine code. An ORG pseudo-operation, for example, causes the assembler to reset its current location pointer to the value specified in its operand field, and assigns that value to the ORG's label if there is one; an EQU pseudo-operation simply assigns a numeric value to a label. A BSS pseudo-operation allocates a specified number of memory locations but does not fill them with anything; a DATA or DEC pseudo-operation allocates memory locations and stores specified values in them.

In an instruction statement, a  $\frac{3}{2}$  appended to the mnemonic forces the assembler to generate this instruction in long (32-bit) form, even though it would normally be generated in short form. The  $\frac{3}{2}$  notation is valid only in V mode. (Short and long form instructions are described in Chapters 8 and 9.)

A  $\underline{\#}$  appended to the mnemonic forces the assembler to generate this instruction in short (16-bit) form, even though it would normally be generated in long form (this can be done only in certain cases; see Chapters 8 and 9 for more information). The # notation is valid only in V mode.

#### Operand Field

The operand field, for those statements that require one, contains the representation of the program element to be acted upon. For a machine instruction it is normally an address expression, and may include indirection, indexing, and base register references. It can also, in certain cases, contain a numeric constant. Refer to <u>TYPES OF</u> <u>ADDRESSING</u> in Chapter 8 (V mode) or Chapter 9 (I mode) of this guide, and to Chapter 3 of the <u>System Architecture Reference Guide</u>. For pseudo-operations, the operand field performs a wide variety of functions, from defining the values of constants to controlling the actions of the linker after assembly is completed. Chapters 4 through 7 detail the actions and operand requirements of pseudo-operations.

<u>Asterisk in the Operand Field</u>: An asterisk in an operand field has two functions. One is to represent an address relative to the current value of the assembler location counter. When used by itself, its value is equal to the displacement, from the beginning of the procedure or linkage segment, of the statement the assembler is currently processing. It is frequently used along with a numeric increment (\*+nn) or decrement (\*-nn) to represent a displacement of <u>nn</u> halfwords relative to the current location. The asterisk's other function is to indicate indirection, with or without indexing; in these cases it always appears following an address, possibly along with an index designator. It is separated from the address by a comma. Indirect addressing is described in Chapters 8 (V mode) and 9 (I mode).

Equal sign in the Operand Field: An equal sign defines a literal value that is to be used by an instruction. A literal is represented as a constant preceded by an equal sign. The following examples show the representations of various kinds of literal operands with a load instruction. In each case, what is loaded is the binary equivalent of the literal operand. If the binary form does not exactly fill the indicated number of bits, it is right-justified with leading zero bits for numeric literals, and left-justified with trailing space characters for character literals. Floating point literals always take exactly the indicated number of bits.

| LDA  | =123     | decimal literal (16 bits)                 |

|------|----------|-------------------------------------------|

| LDL  | =123L    | long decimal literal (32 bits)            |

| LDA  | ='123    | octal literal (16 bits)                   |

| LDA  | =%110010 | binary literal (16 bits)                  |

| LDA  | =\$2FF   | hexadecimal literal (16 bits)             |

| LDA  | =C'AB'   | character literal (16 bits)               |

| LDL  | =C'ABC'  | character literal (32 bits), space-filled |

| LDL  | =C'ABCD' | character literal (32 bits)               |

| LDL  | =Z'ABC'  | character literal (32 bits), zero-filled  |

| LDA  | =EXPR    | literal whose value is expression; see    |

|      |          | the following text                        |

| FLD  | =12.3E4  | single-precision floating point (32 bits) |

| DFLD | =12.3D4  | double-precision floating point (64 bits) |

| QFLD | =12.3Q4  | quad-precision floating point (128 bits)  |

When a literal's value is defined by an expression, any symbols in that expression must be defined by EQU, SET, or XSET statements (described in Chapter 4). The expression's mode must be absolute and its value must be one that can be expressed as a 16-bit integer. (Refer to the discussion of terms and expressions, earlier in this chapter.) If SET or XSET is used to define a symbol, the symbol's value is that computed in the most recent SET or XSET defining that symbol.

#### Note

From the assembler's perspective, the size or type of a data literal does not have to match what is expected by an instruction using the literal. For example, a statement such as LDA =C'ABCD' (a 32-bit literal) is not flagged as an error, although only the first 16 bits of the literal are loaded into the A register (a 16-bit register).

3-12

In V mode, the assembler treats the numeric value of a literal as if it were a label assigned to a constant containing the literal's value. It reserves storage for the constant and stores the constant in that location. The assembler generates the constant's storage address as the operand of the instruction.

In I mode, a number of instructions permit a form of addressing known as <u>immediate</u>. (Refer to <u>Immediate Addressing</u>, in Chapter 9.) If an instruction allows immediate addressing and the literal value is expressible in 16 bits, the literal is stored in the second halfword of the instruction itself; otherwise it is treated and stored as in V mode.

Refer to the descriptions of the RLIT and FIN pseudo-operations in Chapter 5 for information on how and where literals are stored.

#### Comment Field

The comment field provides space for program documentation. It is generally used to describe the mechanics of a procedure. Unless otherwise noted, any text which begins two or more spaces after the last operand is treated by the assembler as a comment field. In a macro call, a comment field must either begin 10 or more spaces after the last operand, or be preceded by a colon (:).

#### PSEUDO-OPERATIONS

Pseudo-operation statements provide directions to the assembler or to the linker. Unlike machine instructions, they direct the actions of the assembler itself, rather than the actions of the assembled program. Some pseudo-operations generate machine code, but most do not. Those that do, define and allocate storage for data that the program is to use, in the form of data constants, address constants, or reserved areas for data storage or buffers.

Pseudo-operation functions described in this guide are of several classes. A list of these classes, and the chapters in which their detailed descriptions appear, follows.

Assembly control (Chapter 4) AC AD Address definition (Chapter 5) CA Conditional assembly (Chapter 4) DD Data definition (Chapter 5)  $\mathbf{LC}$ Listing control (Chapter 4) Literal control (Chapter 5)  $\mathbf{LT}$ Loader control (Chapter 6) LO MD Macro definition (Chapter 7) PLProgram linking (Chapter 6) SA Storage allocation (Chapter 5) SD Symbol definition (Chapter 4)

Table 3-1 contains an alphabetical listing of all the pseudo-operations, their functional class and their restrictions, if any.

All pseudo-operations have an operation field; most also have an operand field, separated from the operation field by spaces. Labels are usually optional, but some pseudo-operations either require a label to be present, or prohibit it.

The operation field contains the mnemonic name that identifies the pseudo-operation.

The operand field, for those pseudo-operations that require one, can contain one or more terms separated by single spaces or commas. Terms can be constants, symbols, or expressions as defined earlier in this chapter. In certain operations, such as BCI, terms can also consist of ASCII character strings.

Address expressions are evaluated as 16-bit integer values and used as a 16-bit memory address, unless otherwise stated. Certain statements (DAC and XAC) accept indirect addressing and indexing symbols. These are interpreted according to the addressing mode in effect when they are encountered.

Table 3-1 Pseudo-Operation Summary

~

| Name | Function                            | <u>Class</u> | Comment               |

|------|-------------------------------------|--------------|-----------------------|

| AP   | Argument pointer                    | AD           |                       |

| BACK | Loop back                           | CA           | Macro definition only |

| BCI  | Define ASCII string (blank fill)    | DD           | -                     |

| BCZ  | Define ASCII string (zero fill)     | DD           |                       |

| BES  | Allocate block ending with symbol   | SA           |                       |

| BSS  | Allocate block starting with symbol | . SA         |                       |

| BSZ  | Allocate block set to zeros         | SA           |                       |

| CALL | External subroutine reference       | PL           |                       |

| CENT | Conditional entry                   | LO           |                       |

| COMM | FORTRAN compatible common           | SA           |                       |

| D32I | Use 32I address mode                | LO           |                       |

| D64V | Use 64V address mode                | LO           |                       |

| DAC  | Define 16-bit address constant      | DD           |                       |

| DATA | Define data constant                | DD           |                       |

| DEC  | Define decimal integer constant     | DD           |                       |

| DFTB | Define table block                  | CA           |                       |

| DFVT | Define value table                  | CA           |                       |

| DUII | Define UII                          | LO           |                       |

| DYMN | Define stack-relative symbol        | SD           |                       |

| DYNT | Direct entry definition             | PL           |                       |

| ECB  | Entry control block                 | PL           |                       |

| EJCT | Eject page                          | LC           |                       |

| ELM  | Enter loader mode                   | LO           |                       |

| ELSE | Reverse conditional assembly        | CA           |                       |

| END  | End of source statements            | AC           |                       |

| ENDC | End conditional assembly area       | CA           |                       |

| ENDM | End macro definition                | MP           | Macro definition only |

| ENT  | Define entry point                  | PL           | -                     |

| EQU  | Fixed symbol definition             | SD           |                       |

| EXT  | External reference                  | PL           |                       |

| FAIL | Force error message                 | CA           |                       |

| FIN  | Insert literals                     | LT           |                       |

| GO   | Forward reference                   | CA           |                       |

| HEX  | Define hexadecimal integer constant |              |                       |

| IFTT | If table true                       | CA           |                       |

| IFTF | If table false                      | CA           |                       |

| IFVT | If value true                       | CA           |                       |

| IF   | If true                             | CA           |                       |

| IFx  | Arithmetic conditional if           | CA           |                       |

| IP   | Indirect pointer                    | AD           |                       |

| LINK | Put code in linkage segment         | AC           |                       |

| LIR  | Load if required                    | LO           |                       |

| LIST | Enable listing                      | LC           |                       |

| LSMD | List macro expansions data only     | LC           |                       |

| LSTM | List macro expansions               | LC           |                       |

| Name | Function                            | <u>Class</u>  | Comment                                         |

|------|-------------------------------------|---------------|-------------------------------------------------|

| MAC  | Begin macro definition              | MP            | Macro definition only                           |

| NLSM | Don't List macro expansions         | LC            | 2                                               |

| NLST | Inhibit listing                     | LC            |                                                 |

| OCT  | Define octal integer constant       | DD            |                                                 |

| ORG  | Define origin location              | AC            |                                                 |

| PCVH | Print cross reference values in HEX | LC            |                                                 |

| PROC | Put code in procedure segment       | AC            |                                                 |

| RLIT | Optimize literals                   | $\mathbf{LT}$ |                                                 |

| SAY  | Print message                       | MP            |                                                 |

| SCT  | Select code within macro            | MP            |                                                 |

| SCTL | Select code from macro list         | MP            |                                                 |

| SEG  | Segmentation assembly V-mode        | AC            | Must be first<br>statement in<br>source program |

| SEGR | Segmentation assembly I-mode        | AC            | Must be first<br>statement in<br>source program |

| SET  | Changeable symbol definition        | SD            |                                                 |

| SETB | Set base sector                     | LO            |                                                 |

| SUBR | Define entry point                  | PL            |                                                 |

| SYML | Allow eight-character symbols       | PL            |                                                 |

| VFD  | Define variable fields              | DD            |                                                 |

| XAC  | External address definition         | AD            |                                                 |

| XSET | Changeable symbol defintion         | SD            |                                                 |

# Table 3-1 (continued) Pseudo-Operation Summary

# MACHINE INSTRUCTIONS

Machine instruction statements generate the instructions that the assembled program is to execute. Machine instructions described in this guide are divided into several groups:

- Generic

- Branch and jump

- Memory reference

- Decimal

- Floating point

- Character

- Process control

- Restricted

All machine instructions are described in Chapters 8, 9, and 10 (for V, I, and IX modes respectively). A summary chart of all instructions for these modes is given in Appendix B.

#### RECOMMENDED PROGRAM STRUCTURE

PMA makes using the segmented architecture easy. The programmer can write straightforward code, such as LDA ADDR; the assembler, depending on the definition of ADDR, may generate a short or long instruction and may reference the stack area, the linkage area, the procedure area, or a temporary area. This is possible because symbols, during assembly, carry a great deal of state information with them.

The structure of a V-mode or I-mode program should reflect the system architecture design for the separation of code and data. The recommended structure is:

# Prologue

| SEG/SEGR | Indicates segmented addressing in V/I mode |

|----------|--------------------------------------------|

| RLIT     | Puts literals in the procedure area        |

| COMM     | Declares FORTRAN-compatible COMMON areas   |

| ENT      | Declares entry point(s) to this program    |

# Procedure/Stack Area

Executable code and dynamic storage

# Data Area

- LINK Defines linkage area containing static variables

- ECB Declares entry control block for this program

#### End

#### END Terminates assembly

All of the above declarations are pseudo-operations. Descriptions of these and other pseudo-operations appear in Chapters 4 through 7 of this guide.

# 4 Code Generation Pseudo-Operations

This chapter describes a group of pseudo-operations that control such things as the placement of generated code within a program (AC), equating symbols to absolute numeric values (SD), and conditional assembly of blocks of statements (CA). Assembly listing control pseudo-operations (LC) are also included in this chapter.

## ASSEMBLY CONTROL PSEUDO-OPERATIONS (AC)

Assembly control pseudo-operations affect the placement of generated code and the addressing mode in which it is generated. The statements in this group are listed below.

| Name | Function                       | Restrictions                           |

|------|--------------------------------|----------------------------------------|

| END  | End of source statements.      |                                        |

| LINK | Put code in linkage segment.   |                                        |

| ORG  | Define origin location.        |                                        |

| PROC | Put code in procedure segment. |                                        |

| SEG  | Segmented assembly (V mode).   | Must appear before any generated code. |

| SEGR | Segmented assembly (I mode).   | Must appear before any generated code. |

[label] END [address-expression]

Terminates assembly of the source program. All literals accumulated since either the start of the program, or the last FIN statement, are assigned locations starting at the current location count. Refer to FIN and RLIT pseudo-operations in Chapter 5 for specific information on how these statements can affect literal placement.

The label field is permitted, but it serves no useful purpose and is usually omitted. While <u>address-expression</u> is indicated as optional, it is required for a main program, that is, the module that contains the entry point of the executable program called from the command processor. The address expression is the label specified in the ECB statement that defines the entry control block for this program. The typical sequence is:

BEGIN first executable instruction . . . LINK static data declarations . . . ECB\_LOC ECB BEGIN END ECB\_LOC

End statements for modules called as subroutines do not need an operand; these modules' entry points are declared in any of several ways, as described in Chapter 12, USING SUBROUTINES.

## LINK

Places subsequent code in the linkage segment. The assembler's location counter mode is set to linkage relative and its value is set to one more than the highest value previously used in the linkage area. It starts at linkage-relative address '400. Linkage-relative mode is terminated by a PROC or COMM pseudo-operation.

The LINK pseudo-operation requires neither a label field nor an operand field.

## [label] ORG address-expression

Sets the assembler location counter equal to the mode and value of <u>address-expression</u>. Symbolic terms in the expression must have been previously defined. An expression containing an asterisk sets the mode and value to the current mode and value of the current location counter. The value may be modified by any terms that have absolute values, such as constants or symbols equated to constants.

The mode of the address expression may be absolute, procedure relative, linkage relative, or common, depending on the mode that was in effect when any symbolic term in <u>address-expression</u> was defined. The value of the location counter is set to the value of the address expression. If the mode of the address expression is absolute, then the mode of the location counter remains unchanged. In all other cases, whether relative, linkage, or common, both the mode and the value of the location counter are set to that of the address expression.

If a label appears in the label field, both the value and mode of the address expression are assigned to that label.